EP1C4F400C8 FPGA: Funktionen, Spezifikationen, Programmierungen und Alternativen

Wenn Sie mit programmierbarer Logik arbeiten, erhalten Sie mit dem EP1C4F400C8 ein praktisches Gleichgewicht zwischen Leistung und Kosten.In diesem Artikel erfahren Sie, was diese FPGA ist, seine wichtigsten Funktionen wie Logikkapazität, Speicher und E/A -Optionen sowie wie seine Struktur zuverlässiges Design unterstützt.Sie werden auch seine Spezifikationen, Anwendungen in Systemen, den Programmierungsprozess und den Vergleich mit ähnlichen Teilen sehen.Katalog

Was ist der EP1C4F400C8?

Der EP1C4F400C8 ist Mitglied der Cyclone FPGA-Familie von Intel (ehemals Altera), die als kostengünstige und zuverlässige programmierbare Logiklösung entwickelt wurde.Dieses Gerät baut auf einem 0,13 uM SRAM-Prozess ein und bietet eine moderate Logikdichte und flexible E/A-Optionen innerhalb eines kompakten FBGA-400-Pakets.Die Cyclone -Familie, die Geräte wie EP1C3, EP1C6, EP1C12 und EP1C20 enthält, wurde erstellt, um die Leistung und Erschwinglichkeit für skalierbare Designs auszugleichen und eine einfache Migration zwischen Dichteniveaus und Paketen zu ermöglichen.Bekannt für Stabilität und umfassende Einführung, bleibt es eine vertrauenswürdige Wahl in Legacy -Designs.

Auf der Suche nach EP1C4F400C8?Kontaktieren Sie uns, um die aktuellen Aktien, die Vorlaufzeit und die Preisgestaltung zu überprüfen.

EP1C4F400C8 CAD -Modelle

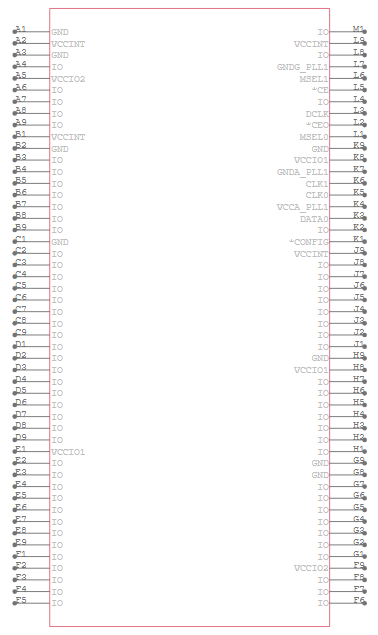

EP1C4F400C8 -Symbol

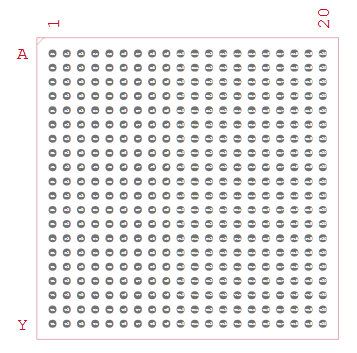

EP1C4F400C8 Footprint

EP1C4F400C8 3D -Modell

EP1C4F400C8 -Funktionen

• Logikkapazität

Der EP1C4F400C8 bietet rund 4.000 Logikelemente, die in 400 Logikarray -Blöcke (Labors) organisiert sind.Dies macht es für Mittelklasse-Designs geeignet, die eine mäßige Logikdichte erfordern und gleichzeitig die Kosteneffizienz beibehalten.

• Eingebetteter Gedächtnis

Es integriert ungefähr 76,5 Kbits eingebetteter Speicher.Dieser interne RAM unterstützt Datenpufferung, Speicher und kleine Speicherfunktionen und verringert die Notwendigkeit externer Speicherkomponenten in vielen Designs.

• Hohe E/O -Zählung

Das Gerät bietet 301 Benutzer-konfigurierbare E/A-Stifte in seinem 400-Ball-FBGA-Paket.Diese hohe Pin -Anzahl ermöglicht eine umfangreiche Konnektivität für komplexe Systeme, die mehrere periphere Schnittstellen erfordern.

• Breite Unterstützung der E/A -Standards

Es unterstützt mehrere E/A-Standards, einschließlich LVTTL, LVCMOS, SSTL-2, SSTL-3 und Differential LVDs.Diese Flexibilität ermöglicht es der FPGA, sich direkt mit einer Vielzahl moderner Logikfamilien und Speichergeräte zu verbinden.

• Hochgeschwindigkeitsdifferentialsignalisierung

Mit der Unterstützung von LVDs bis zu 640 Mbit / s wird die FPGA schnelle Datenübertragungsanforderungen erfüllt.Dies macht es für Anwendungen wie Hochgeschwindigkeitskommunikationsverbindungen und schnelle digitale Schnittstellen praktisch.

• Uhr Management mit PLLS

Der Chip integriert zwei Phasenverschlüsse (PLLS) und acht globale Uhrennetzwerke.Diese Funktionen ermöglichen eine präzise Uhrerzeugung, -multiplikation und Jitter-Steuerung für zeitkritische Anwendungen.

• Niedrigspannungskernbetrieb

Die Geräte, die bei einer nominalen 1,5 -V -Kernspannung betrieben wird, gleicht die Leistung mit geringerem Stromverbrauch aus.Dieser Spannungsniveau wurde für die bei seiner Herstellung verwendete 0,13-µm-CMOS-Technologie optimiert.

• Flexible E/A -Spannungen

Das FPGA unterstützt E/A -Spannungen von 1,5 V, 1,8 V, 2,5 V und 3,3 V über verschiedene Banken.Diese Vielseitigkeit ermöglicht es, sowohl mit Legacy als auch mit modernen Systemkomponenten zu verbinden.

• SRAM-basierte Konfiguration

Wie bei anderen Cyclone-FPGAs ist es SRAM-basiert und erfordert bei jedem Stromverbrauch eine Neukonfiguration.Dies bietet Flexibilität für Aktualisierungen, erfordert jedoch auch ein externes Konfigurationsgerät oder ein Controller.

• Bitstream -Kompressionsunterstützung

Das EP1C4F400C8 unterstützt während der Konfiguration eine komprimierte Bitstream -Belastung.Dies reduziert die Anforderungen an die externen Speicher und beschleunigt die Konfigurationszeiten.

• PCI -Konformität

Es umfasst eine integrierte Unterstützung für PCI-Standards (33/66 MHz, 32/64-Bit).Mit dieser Funktion kann das Gerät direkt in Systeme integriert werden, die PCI -Schnittstellen ohne zusätzliche Überbrückungslogik benötigen.

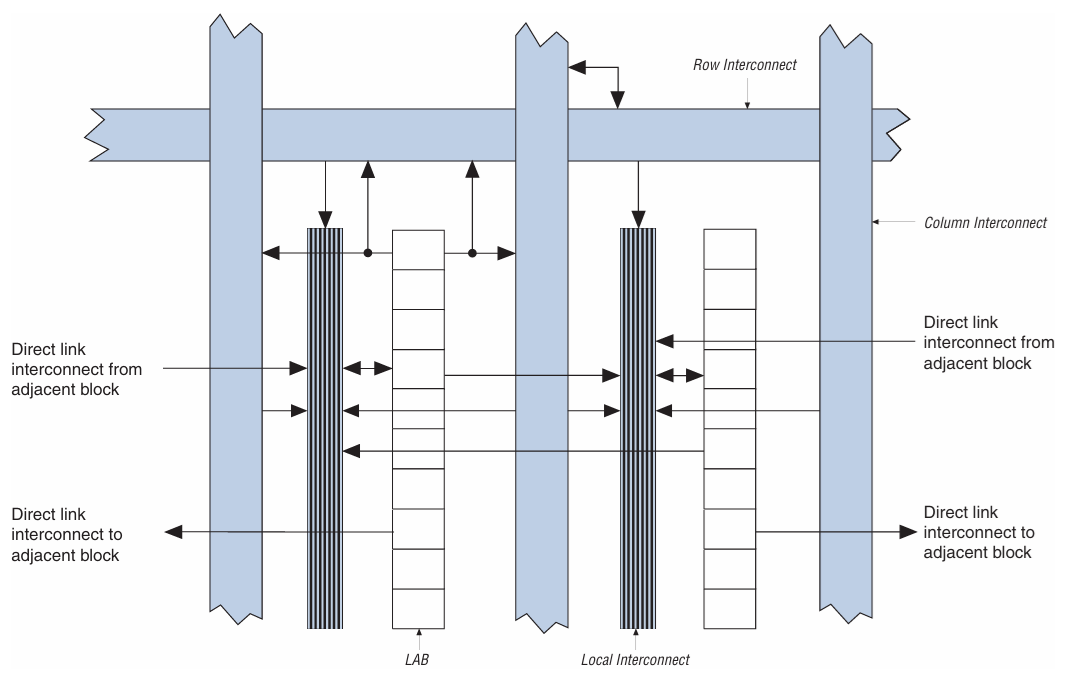

Zyklonlaborstruktur

Das Diagramm zeigt die LAB -Struktur (Logic Array Block), die in Cyclon -FPGAs wie dem EP1C4F400C8 verwendet wird.Jedes Labor stellt eine Verbindung zu einem Netzwerk von Interconnects her: Zeilenverbindungen, Spaltenverbindungen und lokale Verbindungen, die Signale zwischen Logikelementen und anderen Blöcken leiten.Direkte Verbindungsverbindungen bieten benachbarte Labors schnelle, niedrige Latenzwege und verbessert die Zeitleistung in Signalpfaden.Diese Architektur ist wichtig, da sie die Routing -Flexibilität mit Effizienz ausgleichen, sodass die FPGA komplexe Designs bewältigen und gleichzeitig die Geschwindigkeit und die Fläche optimieren können.

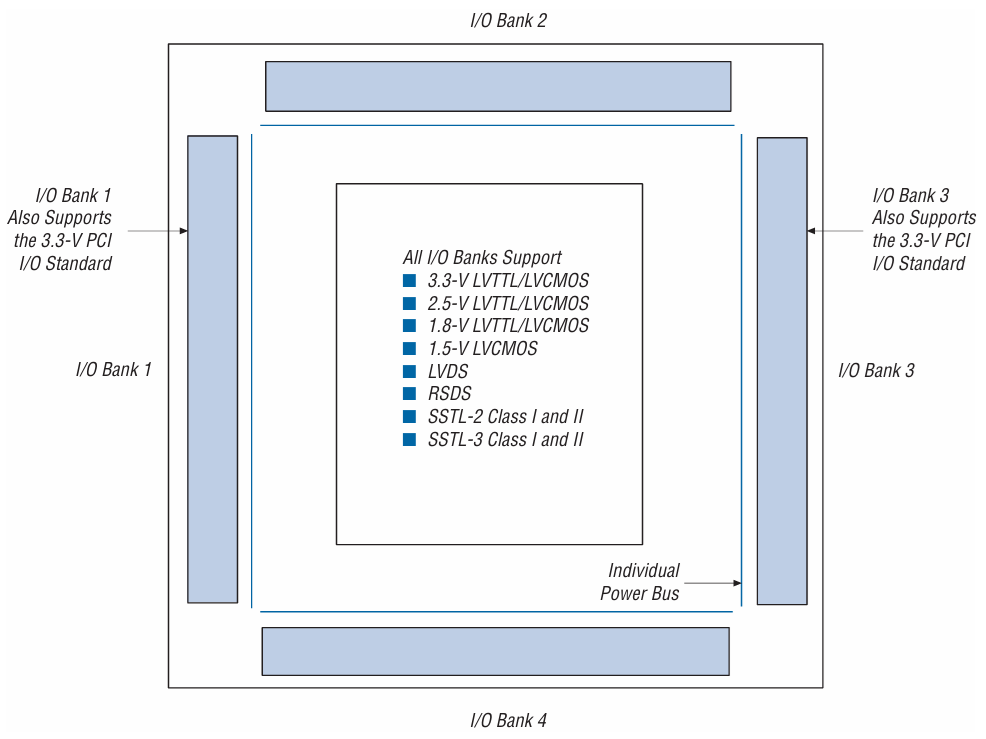

Zyklon -E/A -Bankendiagramm

Das Diagramm zeigt die E/A -Bankstruktur von Cyclon -FPGAs wie dem EP1C4F400C8.Das Gerät ist in vier E/A -Banken unterteilt, die jeweils von seinem eigenen Versorgungsbus angetrieben werden, wodurch verschiedene Spannungsstandards innerhalb eines einzelnen FPGA gemischt werden können.Alle Banken unterstützen eine breite Palette von E/A-Standards, einschließlich LVTTL, LVCMOS, LVDS, RSDS und SSTL, während die Banken 1 und 3 auch 3,3-V-PCI für die Kompatibilität mit Legacy-Systemen unterstützen.Diese flexible E/O -Architektur ist wichtig, da sie eine nahtlose Integration in verschiedene externe Geräte und Schnittstellen ermöglicht, wodurch die FPGA an verschiedene Anwendungen anpassbar ist.

EP1C4F400C8 -Spezifikationen

|

Typ |

Parameter |

|

Hersteller |

Altera/Intel |

|

Serie |

Cyclone® |

|

Verpackung |

Tablett |

|

Teilstatus |

Veraltet |

|

Anzahl der Labors/CLBs |

400 |

|

Anzahl der logischen Elemente/Zellen |

4000 |

|

Gesamt -Ram -Bits |

78.336 |

|

Anzahl von i/o |

301 |

|

Spannung - Versorgung |

1,425 V ~ 1,575 V |

|

Montagetyp |

Oberflächenhalterung |

|

Betriebstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Paket / Fall |

400-bga |

|

Lieferantengerätepaket |

400-FBGA (21 × 21) |

|

Grundproduktnummer |

EP1C4 |

EP1C4F400C8 -Anwendungen

1. digitale Signalverarbeitung (DSP)

Der EP1C4F400C8 kann so programmiert werden, dass sie Aufgaben wie Filterung, FFT und Signalmodulation ausführen.Die Kombination aus Logikelementen und eingebettetem Speicher macht es für die Hochgeschwindigkeitsverarbeitung geeignet.Auf diese Weise kann es herkömmliche DSP -Chips durch eine flexible FPGA -Lösung ersetzen, die für verschiedene Algorithmen neu programmiert werden kann.

2. Eingebettete und Steuerungssysteme

In industriellen und eingebetteten Systemen wird diese FPGA häufig verwendet, um benutzerdefinierte Controller, Sequenzer und Zustandsmaschinen zu implementieren.Die rekonfigurierbare Logik ermöglicht es, das Hardwareverhalten genau auf die Systemanforderungen anzupassen.Durch die Integration der Kontrolllogik in das FPGA wird die Anzahl der externen Komponenten reduziert, was die Zuverlässigkeit und die Senkung der Kosten verbessert.

3. Überbrückung von Kommunikation und Schnittstelle

Das Gerät unterstützt mehrere E/A -Standards und kann als Brücke zwischen verschiedenen Kommunikationsprotokollen fungieren.Es wird häufig verwendet, um PCI, LVDs, SDRAM und andere Schnittstellen nahtlos innerhalb eines Systems zu verbinden.Dies macht es bei Networking-Geräten, eingebetteten Controllern und Umbauten von Legacy-to-Modern-Schnittstellen sehr nützlich.

4. Datenerfassung und -verarbeitung

Mit hoher E/A-Verfügbarkeit und flexibles Speicher ist der EP1C4F400C8 für Datenerfassungssysteme gut geeignet.Es kann direkt mit ADCs und Sensoren verknüpfen, die Daten rechtzeitig verarbeiten und sie für die Speicherung oder Übertragung vorbereiten.Solche Anwendungen sind in medizinischen Instrumenten, Testgeräten und wissenschaftlichen Messgeräten üblich.

EP1C4F400C8 Ähnliche Teile

|

Spezifikation |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Hersteller |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

FPGA -Familie |

Zyklon (EP1C4) |

Zyklon (EP1C4) |

Zyklon (EP1C4) |

Zyklon (EP1C4) |

Zyklon (EP1C4) |

Zyklon (EP1C4) |

|

Logikelemente (LES) |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

|

Eingebetteter Speicher (Bits) |

~ 76,5 Kbits |

~ 76,5 Kbits |

~ 76,5 Kbits |

~ 76,5 Kbits |

~ 76,5 Kbits |

~ 76,5 Kbits |

|

E/O -Stifte |

301 |

301 |

301 |

301 |

249 |

97 |

|

Paket / Fall |

400-fbga |

400-fbga |

400-fbga |

400-fbga |

324-fbga |

144-TQFP |

|

Geschwindigkeitsqualität |

C8 |

C8 |

C8 |

C6 (schneller) |

C8 |

C8 |

|

Kernspannung |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

|

Betriebstemperatur.Reichweite |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C.

|

EP1C4F400C8 -Programmierschritte

Bevor Sie den EP1C4F400C8 FPGA verwenden können, müssen Sie Ihr Design in das Gerät laden.Bei der Programmierung werden die FPGA mit einer Bitstream -Datei konfiguriert, damit sich sie als beabsichtigte Schaltung verhalten kann.

1. Wählen Sie das Konfigurationsschema aus und setzen Sie MSEL -Pins fest

Sie beginnen mit der Auswahl des Konfigurationsschemas, das am besten zu Ihrem Setup passt, z. B. aktive serielle, passive Serien oder JTAG.Dies erfolgt durch Einstellen der MSEL-Stifte vor dem Einschalten auf bestimmte Logikniveaus.In jedem Modus werden verschiedene Pins und Protokolle verwendet, sodass Sie die Kompatibilität mit Ihren Entwurfstools und Ihrem Konfigurationsspeicher bestätigen müssen.Die richtige Auswahl hier sorgt für einen reibungslosen Konfigurationsprozess.

2. Wenden Sie Strom an und initialisieren Sie das Gerät

Schalten Sie den Kern- und I/A -Schienen des FPGA in den angegebenen Spannungsbereichen ein.Halten Sie beim Start den Nconfig -Stift niedrig, um das Gerät im Reset zu halten, bis die Versorgungsspannungen stabil sind.Sobald Sie stabil sind, werden Sie zurückgesetzt und die Geräte signalisiert die Bereitschaft, indem Sie den Nstatus -Pin fahren.Dies garantiert, dass die FPGA vor Beginn der Konfiguration ordnungsgemäß initialisiert wird.

3. Senden Sie den Konfigurationsbitstream

In dieser Phase senden Sie die Konfigurationsdatendatei (Bitstream) mit Ihrem ausgewählten Schema an die FPGA.Im aktiven seriellen oder passiven seriellen Modus stammt der Bitstream von einem externen Speichergerät, während JTAG eine direkte Programmierung über Kabel ermöglicht.Das Gerät liest kontinuierlich in den Konfigurationsdaten, bis es abgeschlossen ist.Ihre Designsoftware generiert diesen Bitstream, um Ihren Logikanforderungen zu entsprechen.

4. Bestätigen Sie eine erfolgreiche Konfiguration (conf_done)

Wenn das FPGA das Laden beendet, wird der Conf_Done -PIN geltend gemacht, um anzuzeigen, dass Konfigurationsdaten erfolgreich empfangen wurden.Gleichzeitig führt das Gerät eine interne Initialisierung durch, z. B. Löschen von Registern und Aktivierung von E/A.Wenn Conf_Done nicht hoch ist, bedeutet dies normalerweise, dass die Konfigurationsdaten oder ein Setup einen Fehler aufweisen.Das Beobachten dieser PIN ist der einfachste Weg, um zu überprüfen, ob der Vorgang abgeschlossen ist.

5. Führen Sie eine optionale Rekonfiguration im System durch

Schließlich haben Sie die Möglichkeit, das FPGA zu aktualisieren oder neu zu programmieren, ohne sie aus der Karte zu entfernen.Mit JTAG oder einem eingebetteten Controller können Sie einen neuen Bitstream direkt laden, was für Firmware -Updates nützlich ist.Mit dieser Flexibilität können Sie Ihr System auch nach der Bereitstellung ändern, debuggen oder aktualisieren.Es stellt sicher, dass sich Ihr FPGA-basiertes Design im Laufe der Zeit an sich ändernde Anforderungen anpassen kann.

EP1C4F400C8 Vor- und Nachteile

Vorteile

• Kosteneffiziente Auswahl für Mittelklasse-Designs

• Hohe E/A -Anzahl im Vergleich zu ähnlichen Dichtegeräten

• Flexible Spannung und E/A -Standardunterstützung

• unterstützt durch reife Werkzeuge und Dokumentation

• Niedrigere Leistung als ältere FPGA -Generationen

Nachteile

• veraltet mit begrenzter langfristiger Verfügbarkeit

• niedrigere Logik- und Speicherkapazität im Vergleich zu modernen FPGAs

• Langsamere Betriebsgeschwindigkeit und E/A -Leistung

• Erfordert externe Speicher für die Konfiguration beim Einschalten

• Fehlen fortschrittliche Funktionen wie DSP-Blöcke und Hochgeschwindigkeitsübertragungen

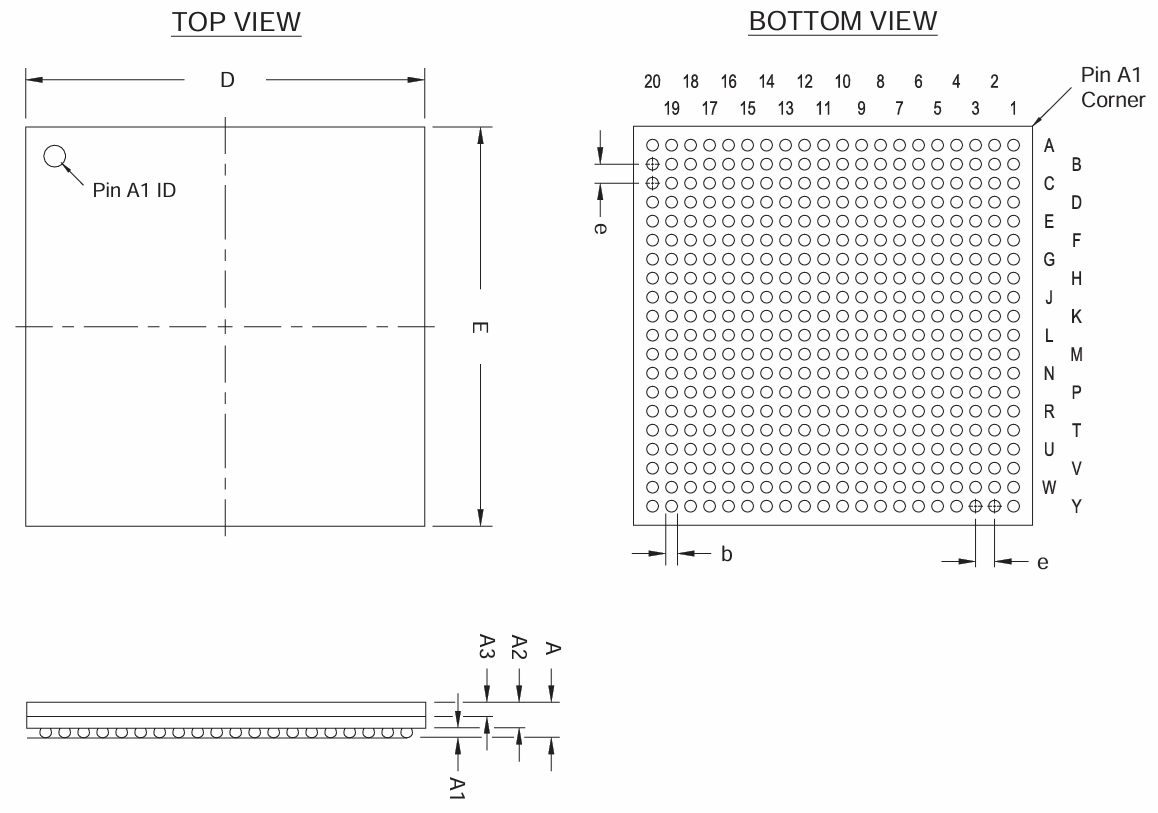

EP1C4F400C8 Verpackungsabmessungen

|

Typ |

Parameter |

|

Paketart |

FBGA (Fine-Pitch-Kugel-Gitter-Array) |

|

Ballzahl |

400 |

|

Ball Tonhöhe (e) |

1,0 mm (typisch für Cyclone EP1C4F400) |

|

Kugeldurchmesser (b) |

0,45 mm (nominal) |

|

Paketgröße (D × E) |

21 mm × 21 mm |

|

Pakethöhe (a) |

2,40 mm (max) |

|

Substratdicke (A2) |

~ 0,40 mm |

|

Schimmelpackdicke (A3) |

~ 1,90 mm |

|

Ballhöhe (A1) |

0,25 mm (nominal) |

|

Pin A1 Ecke |

Markiert zur Orientierung |

|

Array -Layout |

20 × 20 Gitter (mit fehlenden Eckbällen) |

|

Montage |

Oberflächenhalterung (SMD) |

EP1C4F400C8 Hersteller

Der EP1C4F400C8 wurde ursprünglich von hergestellt von Altera Corporation, ein Pionier in programmierbaren Logikgeräten und FPGA -Technologie.Im Jahr 2015 wurde Altera von übernommen von Intel Corporationund die Produktlinie wurde Teil der Intel Programable Solutions Group (PSG).Heute unterstützt Intel diese Legacy -Altera -Geräte und fokussiert die Entwicklung auf neuere FPGA -Familien, sorgt für die Kontinuität bestehender Benutzer und fördert die Innovation in der programmierbaren Logik.

Abschluss

Der EP1C4F400C8 stammt als kostengünstige und vielseitige FPGA, das eine solide Leistung für Mittelklasse-Designs bietet.Mit seinen 4.000 Logikelementen, dem eingebetteten Speicher, der umfangreichen E/A -Unterstützung und der Kompatibilität mit mehreren Spannungs- und Schnittstellenstandards bietet es Flexibilität für unterschiedliche Anwendungen.Sein Architektur, der Programmierungsprozess und die breite Benutzerfreundlichkeit in DSP, eingebetteten Systemen und Datenerfassung machen es trotz seines Erbezustands zu einer praktischen Wahl.Während es an fortgeschrittenen Funktionen fehlen, die in neueren Geräten zu finden sind und sich nur begrenzte langfristige Verfügbarkeit gegenübersehen, bleibt es eine zuverlässige Option, nach nach nachweislichen Lösungen in skalierbaren FPGA-Designs zu suchen.

Datenblatt PDF

EP1C4F400C8 -Datenblätter:

Über uns

ALLELCO LIMITED

Weiterlesen

Schnelle Anfrage

Bitte senden Sie eine Anfrage, wir werden sofort antworten.

Häufig gestellte Fragen [FAQ]

1. Welche Tools sind erforderlich, um den EP1C4F400C8 zu programmieren?

Sie benötigen die Quartus-Software von Intel sowie ein unterstütztes Programmierkabel wie USB-Blaster.Mit diesen Tools können Sie den Bitstream erstellen und in die FPGA laden.

2. Kann der EP1C4F400C8 PCI -Anwendungen direkt behandeln?

Ja, die Einhaltung von PCI-Standards (33/66 MHz, 32/64-Bit) enthält eine integrierte Einhaltung von PCI-Standards, wodurch es für die PCI-basierte Systemintegration geeignet ist, ohne eine zusätzliche Überbrückungslogik zu erfordern.

3. Was passiert, wenn der EP1C4F400C8 während der Konfiguration fehlschlägt?

Wenn die Konfiguration fehlschlägt, wird der Conf_Done -Pin nicht hoch geltend.Dies weist normalerweise auf einen Fehler in der Bitstream -Datei, der Spannungssequenzierung oder in der PIN -Setup hin und sollte in Ihrem Entwurfsfluss erneut überprüft werden.

4. Kann die EP1C4F400C8 direkt mit dem DDR -Speicher einstellen?

Es unterstützt mehrere E/A -Standards, verfügt jedoch nicht über native DDR -Schnittstellen wie moderne FPGAs.Es können zusätzliche Konstruktionsüberlegungen oder Überbrückungskomponenten erforderlich sein.

5. Wie ist der EP1C4F400C8 mit neueren FPGAs verglichen?

Im Vergleich zu modernen Geräten weist der EP1C4F400C8 eine geringere Geschwindigkeit, eine geringere logische Dichte und weniger fortgeschrittene Funktionen auf.Es bleibt jedoch eine kostengünstige Wahl für stabile, mittlere Konstruktionen, bei denen keine hochmoderne Leistung erforderlich ist.

EPM3256AFC256-7 CPLD-Übersicht: Funktionen, Pinout, Programmierung und Anwendungen

auf 2025/10/3

ADG432BR Analog Switch IC: Spezifikationen, Pinout, Alternativen und Datenblatt

auf 2025/10/2

Beliebte Beiträge

-

Komplexe Anweisungssatzcomputer: Wie verändert sie das Computer?

auf 8000/04/18 147780

-

USB-C-Pinout und Funktionen

auf 2000/04/18 112042

-

Verwenden von Xilinx Unified Simulation Primitive: Ein umfassender Leitfaden für FPGA -Design und -Simulation

auf 1600/04/18 111352

-

Stromversorgungsspannungen in der Elektronik: Bedeutung von VCC, VDD, VEE, VSS und GND

auf 0400/04/18 83798

-

RJ45 -Anschlusshandbuch: Pinbeleg, Kabeltypen und Verwendung

auf 1970/01/1 79604

-

Die ultimative Anleitung zu Farbcodes in modernen elektrischen Systemen

Die Art und Weise, wie unsere elektrischen Systeme Farben verwenden, gilt nicht nur für das Aussehen.Jede Drahtfarbe zeigt nun eine bestimmte Funktion an und erleichtert die Identifizierung und Ver...auf 1970/01/1 66983

-

Leitfaden für Spülventile: Funktion, Symptome, Test und Ersatz für eine optimale Motorleistung

Das Säuberventil ist ein wesentlicher Bestandteil eines Autosystems, mit dem die Luft sauber hält, indem sie Kraftstoffdämpfe verwalten, bevor sie in die Atmosphäre entkommen können.Dies hilft der ...auf 1970/01/1 63113

-

Qualität (q) Faktor: Gleichungen und Anwendungen

Der Qualitätsfaktor oder "Q" ist wichtig, wenn Sie überprüfen, wie gut Induktoren und Resonatoren in elektronischen Systemen funktionieren, die Funkfrequenzen (RF) verwenden.'Q' misst, wie gut ein ...auf 1970/01/1 63048

-

Erreichen der Spitzenleistung mit dem maximalen Stromübertragungssatz

Der maximale Stromübertragungssatz erklärt, wie Energie aus einer Quelle wie einer Batterie oder einem Generator zu einer angeschlossenen Last fließt.Es zeigt die genaue Bedingung, bei der die Last...auf 1970/01/1 54097

-

A23 Batteriespezifikationen und Kompatibilität

Die A23-Batterie ist eine kleine, zylinderförmige Batterie mit hoher Spannung.Auch 23A, 23Ae oder Mn21 genannt, läuft es mit 12 Volt und viel höher als AA- oder AAA -Batterien.Sein besonde...auf 1970/01/1 52199