Verbesserung des FPGA -Designs mit Benutzerbeschränkungsdateien (UCF) für Xilinx ISE -Tools

In diesem Handbuch wird die Rolle von Benutzerbeschränkungsdateien (UCFs) bei der Verbesserung des FPGA -Designs mit Xilinx ISE -Tools untersucht.UCFs ermöglichen es, spezifische Einschränkungen hinzuzufügen, um das Timing, die Logik und die Platzierung besser zu steuern, die die Entwurfsgenauigkeit, die Leistung und die Zuverlässigkeit stärken.Indem der Leitfaden zeigt, wie diese Einschränkungen effektiv angewendet werden können, wird der Entwurfsprozess vereinfacht, die Debugging -Zeit verkürzt und eine erfolgreiche Projektbereitstellung gewährleistet.Katalog

Zweck und Rolle von UCFs im FPGA -Design

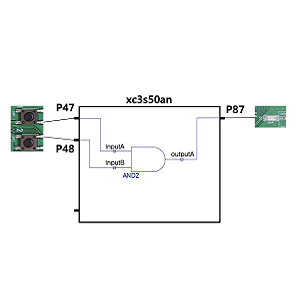

Im FPGA -Design spielen Benutzerbeschränkungsdateien (UCFs) eine Rolle bei der Steuerung der synthetisierten Logik, die aus Ihrem Code synthetisiert wurde, auf dem Chip physikalisch implementiert.Mit diesen Dateien können wichtige Parameter wie Timing -Einschränkungen, PIN -Zuordnungen und Bereiche der Flächenplatzierung direkt angeben, die sich direkt auswirken können, ob ein Design den Leistungsanforderungen entspricht oder nicht.Stellen Sie sich UCFs als Blaupausen vor, die sicherstellen, dass alles richtig positioniert ist, im Zeitplan funktioniert und ordentlich eingerichtet ist.Der Prozess der Einschränkung der Einschränkung beginnt in den frühen Entwicklungsstadien.Erstellen Sie zunächst vor der Synthese eine UCF -Datei, um sicherzustellen, dass die Parameter von Anfang an rechts gesperrt sind.Nach der Synthese werden zusätzliche Einschränkungsdateien wie die NetList Constraint -Datei (NCF) und die physische Einschränkungsdatei (PCF) generiert, um Änderungen an der Logik widerzuspiegeln und die physischen Einschränkungen abzuschließen.Jede dieser Dateien baut auf dem vorherigen Schritt auf und verfeinert das Design schrittweise.UCFs sind textbasierte Dateien, die im ASCII-Format geschrieben wurden. Dies bedeutet, dass sie mit grundlegenden Texteditoren oder spezielleren Tools wie dem Xilinx Constraint-Editor bearbeitet werden können.Diese Einfachheit macht UCFs sehr zugänglich und flexibel, um in die Besonderheiten der Einschränkungen einzusteigen, ohne übermäßig komplexe Werkzeuge zu benötigen.

Wie können Einschränkungen FPGA -Design formen?

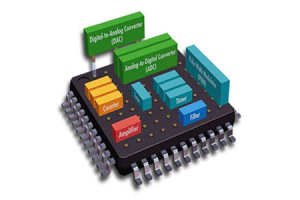

Im FPGA -Design spielen Einschränkungen eine Rolle bei der Gestaltung der Ausführung des Chips und der Interaktion mit externen Geräten.Diese Einschränkungen werden in einer UCF (Benutzerbeschränkungen -Datei) definiert, die als detaillierter Anweisungssatz für das Design -Tool fungiert, in dem angegeben ist, wie die internen Komponenten der FPGA verbunden und verwaltet werden sollten.Zu den wichtigsten Einschränkungen gehören Zeitbeschränkungen, mit denen die Signale zwischen den Komponenten innerhalb eines bestimmten Zeitrahmens wenden, um die zuverlässige Leistung bei der gewünschten Taktgeschwindigkeit aufrechtzuerhalten.PIN -Zuweisungen karten physische FPGA -Stifte externer Geräte wie Sensoren, Speichermodule oder Kommunikationsschnittstellen, wodurch genaue Verbindungen sichergestellt werden.Flächenbeschränkungen steuern die Platzierung von Logikblöcken am Chip, um Staus zu vermeiden, Verzögerungen zu reduzieren und die Ressourcenverbrauch zu optimieren.Ohne diese Einschränkungen würden automatisierte Tools Platzierungs- und Routing -Entscheidungen treffen, jedoch häufig mit suboptimalen Ergebnissen, was zu Zeitproblemen, Engpässen oder ineffizienten Chip -Layouts führt.Durch die Verwendung von UCF -Dateien behalten viele die Kontrolle über diese kritischen Aspekte, was zu einer besseren Leistung, Effizienz und Zuverlässigkeit bei FPGA -Designs führt.

Die iterative Natur der Einschränkung der Verfeinerung

FPGA-Design ist selten ein Ein-und-don-Prozess.Die Einschränkungen werden während des gesamten Entwicklungszyklus wiederholt angepasst, wenn sich das Design entwickelt und neue Herausforderungen entstehen.Andere optimieren UCF -Dateien, um Leistungsziele zu erfüllen, Zeitprobleme zu beheben oder sich an die sich ändernden Projektanforderungen anzupassen.Diese iterative Verfeinerung ist ein wichtiger Bestandteil des FPGA -Workflows.Wenn Sie beispielsweise feststellen, dass ein Signalpfad zu lange dauert, um sich zwischen zwei Komponenten zu vermehren, kann er die UCF ändern, um die Zeitablaufbeschränkung zu ändern, oder diese Komponenten um die Verringerung von Verzögerungen zu verlagern.In ähnlicher Weise kann die UCF bearbeitet werden, um die Nichtübereinstimmung zu beheben, wenn eine PIN -Zuordnung mit externer Hardware in Konflikt steht.Jede Überarbeitung der UCF bringt das Design näher an das gewünschte Ergebnis. Jede Anpassung lehrt mehr über die Kompromisse bei der FPGA-Optimierung.Dieser Zyklus des Tests, Anpassens und Lernens verbessert nicht nur das Design, sondern schärft auch die Fähigkeiten.

Vorteile der Verwendung von UCFs

Die Anwendung von Einschränkungen über UCF -Dateien bietet mehrere praktische Vorteile, die zum Erfolg von FPGA -Projekten beitragen:

• Verbesserte Zeitgenauigkeit: Gut abgestimmte Zeitpunktbeschränkungen stellen sicher, dass die FPGA mit der gewünschten Taktgeschwindigkeit zuverlässig arbeitet und Fehler vermeiden, die durch Signalverzögerungen verursacht werden.

• Bessere Ressourcenauslastung: Flächenbeschränkungen verhindern, dass Logikblöcke zu nahe oder zu weit voneinander entfernt sind, den Chipraum optimieren und die Leistung verbessern.

• Vereinfachtes Debugging: Durch die Kontrolle von PIN -Zuordnungen und Signalrouting helfen UCFs bei der Reduzierung von Routing -Konflikten und erleichtern die Diagnose und Behebung von Problemen während des Tests.

Über uns

ALLELCO LIMITED

Weiterlesen

Schnelle Anfrage

Bitte senden Sie eine Anfrage, wir werden sofort antworten.

Anwendungsspezifische Standardprodukte (ASSPs): Innovation in der modernen Elektronik vorantreiben

auf 2025/01/8

System auf einem programmierbaren Chip (SOPC): Technologie, Design und Anwendungen

auf 2025/01/8

Beliebte Beiträge

-

Komplexe Anweisungssatzcomputer: Wie verändert sie das Computer?

auf 8000/04/18 147776

-

USB-C-Pinout und Funktionen

auf 2000/04/18 112018

-

Verwenden von Xilinx Unified Simulation Primitive: Ein umfassender Leitfaden für FPGA -Design und -Simulation

auf 1600/04/18 111351

-

Stromversorgungsspannungen in der Elektronik: Bedeutung von VCC, VDD, VEE, VSS und GND

auf 0400/04/18 83777

-

RJ45 -Anschlusshandbuch: Pinbeleg, Kabeltypen und Verwendung

auf 1970/01/1 79575

-

Die ultimative Anleitung zu Farbcodes in modernen elektrischen Systemen

Die Art und Weise, wie unsere elektrischen Systeme Farben verwenden, gilt nicht nur für das Aussehen.Jede Drahtfarbe zeigt nun eine bestimmte Funktion an und erleichtert die Identifizierung und Ver...auf 1970/01/1 66964

-

Leitfaden für Spülventile: Funktion, Symptome, Test und Ersatz für eine optimale Motorleistung

Das Säuberventil ist ein wesentlicher Bestandteil eines Autosystems, mit dem die Luft sauber hält, indem sie Kraftstoffdämpfe verwalten, bevor sie in die Atmosphäre entkommen können.Dies hilft der ...auf 1970/01/1 63104

-

Qualität (q) Faktor: Gleichungen und Anwendungen

Der Qualitätsfaktor oder "Q" ist wichtig, wenn Sie überprüfen, wie gut Induktoren und Resonatoren in elektronischen Systemen funktionieren, die Funkfrequenzen (RF) verwenden.'Q' misst, wie gut ein ...auf 1970/01/1 63041

-

Erreichen der Spitzenleistung mit dem maximalen Stromübertragungssatz

Der maximale Stromübertragungssatz erklärt, wie Energie aus einer Quelle wie einer Batterie oder einem Generator zu einer angeschlossenen Last fließt.Es zeigt die genaue Bedingung, bei der die Last...auf 1970/01/1 54097

-

A23 Batteriespezifikationen und Kompatibilität

Die A23-Batterie ist eine kleine, zylinderförmige Batterie mit hoher Spannung.Auch 23A, 23Ae oder Mn21 genannt, läuft es mit 12 Volt und viel höher als AA- oder AAA -Batterien.Sein besonde...auf 1970/01/1 52189