XC2C256-7TQ144C CPLD: Pinout-, Funktionen, Programmier- und Datenblatthandbuch

In dieser Anleitung erhalten Sie einen klaren Blick auf den XC2C256-7TQ144C, eine CPLD mit niedriger Leistung aus der Coolinx-Familie von Xilinx (jetzt AMD).Sie erfahren über die PIN-Konfiguration, die CAD-Modelle und die Hauptfunktionen wie Logikkapazität, E/A-Optionen, Spannungsunterstützung und Leistungssparfunktionen.Wir werden auch die Architektur, I/V -Kurve und Spezifikationen durchlaufen, gefolgt von Anwendungen, ähnlichen Teilen, Programmierschritten, Vor- und Nachteilen, Verpackungsdetails und Herstellerinformationen, damit Sie genau verstehen können, wie dieses Gerät in Ihre Projekte passt.Katalog

Was ist der XC2C256-7TQ144C?

Der XC2C256-7TQ144C ist eine Low-Power-CPLD (komplexes programmierbares Logikgerät) aus der Coolinx-Familie von Xilinx, die jetzt Teil von AMD ist.Es verfügt über 256 Makrozellen und wird in einem 144-poligen TQFP-Paket erhältlich, das für einen schnellen, deterministischen Betrieb mit minimalem Stromverbrauch ausgelegt ist.Wenn es auf einem 1,8-V-Kern arbeitet, bietet es eine zuverlässige Leistung in einem kompakten Formfaktor und eignet sich gut für Entwürfe, die sofortige Funktionen und effiziente Logikimplementierung erfordern.Im Rahmen der vielseitigen Coolrunner-II-Serie profitiert sie von einer bewährten Architektur und einer umfassenden Designkompatibilität.

Auf der Suche nach XC2C256-7TQ144C?Kontaktieren Sie uns, um die aktuellen Aktien, die Vorlaufzeit und die Preisgestaltung zu überprüfen.

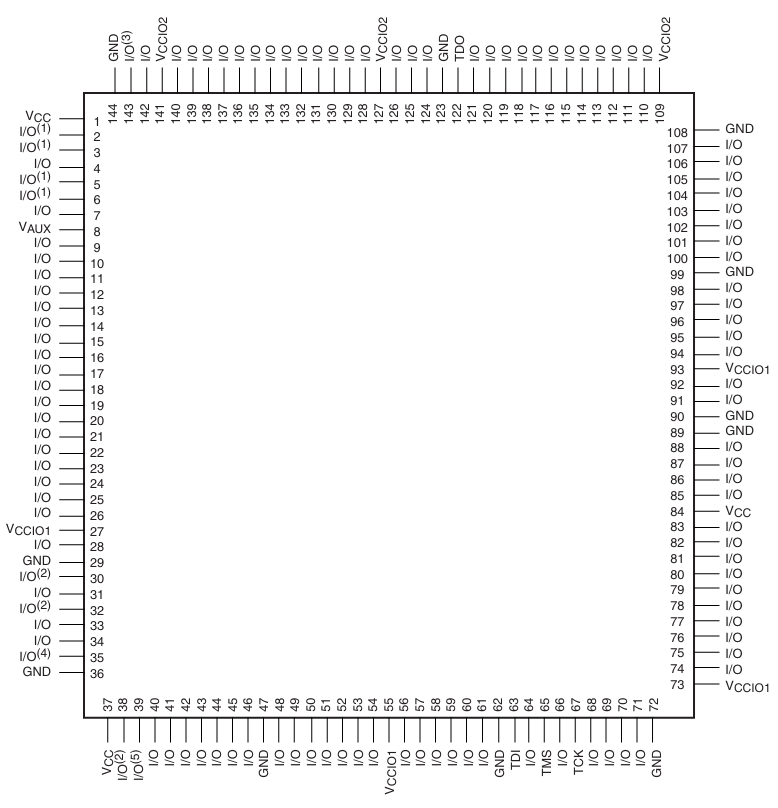

XC2C256-7TQ144C Pin-out-Diagramm

Das XC2C256-7TQ144C-Pin-out-Diagramm zeigt, wie die 144 Stifte für Strom-, Boden-, JTAG- und benutzerprogrammierbare E/A-Funktionen angeordnet sind.Die meisten Stifte sind E/A, die als Eingänge oder Ausgänge konfiguriert werden können und gleichmäßig verteilt werden, um flexible Routing zu unterstützen.VCC, VCCIO1, VCCIO2, VAUX und GND -PINs werden um das Paket platziert, um eine stabile Stromverteilung und mehrere E/A -Spannungsoptionen bereitzustellen.Die JTAG-Stifte (TDI, TDO, TMS, TCK) werden für eine einfache Programmierung und Prüfung im System zusammengefasst.

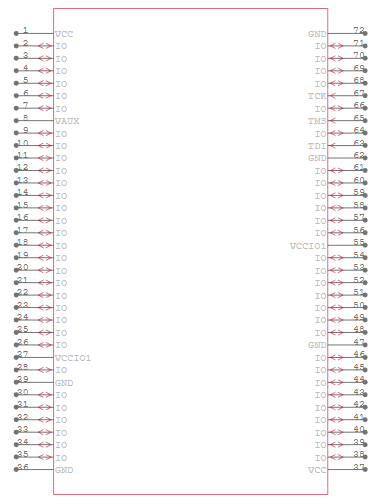

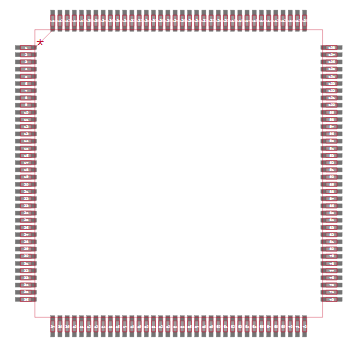

XC2C256-7TQ144C CAD-Modelle

XC2C256-7TQ144C-Symbol

XC2C256-7TQ144C Footprint

XC2C256-7TQ144C 3D-Modell

XC2C256-7TQ144C-Funktionen

• Gerätetyp und Familie

Das XC2C256-7TQ144C ist ein komplexes programmierbares Logikgerät (CPLD), das zur von Xilinx (jetzt AMD) entwickelten Coolrunner-II-Familie gehört.Es ist für einen geringen Stromverbrauch konzipiert und gleichzeitig eine schnelle, deterministische Logikleistung aufrechterhalten, wodurch es ideal für die Kontrolllogik und die Schnittstellenanwendungen.

• Logikkapazität

Dieses Gerät enthält 256 Makrozellen, bei denen es sich um die programmierbaren Ressourcen in der CPLD handelt.Diese Makrozellen können so konfiguriert werden, dass verschiedene kombinations- und sequentielle Logikfunktionen implementiert werden, wodurch eine mäßige Kapazität für Steuerung, Kleberlogik und Busoberflächen vermittelt werden.

• Logikblöcke (Funktionsblöcke)

Es integriert 16 Funktionsblöcke, die Gruppen von Makrozellen organisieren und verwalten.Jeder Block bietet lokale Verbindungs- und Produktressourcen, die eine flexible logische Implementierung und eine effiziente Routing innerhalb des Geräts ermöglichen.

• Benutzer -E/A -Stifte

Der XC2C256-7TQ144C bietet bis zu 118 Benutzer-konfigurierbare E/A-Stifte in seinem TQFP-144-Paket.Mit dieser hohen Pin-Anzahl können das Gerät gleichzeitig mit mehreren Subsystemen Schnittstellen und es für komplexe Designs auf Brettebene geeignet ist.

• Kernspannung (VCC)

Der Kern arbeitet bei einem nominalen Bereich von 1,8 V (1,7 V bis 1,9 V), wodurch der Stromverbrauch im Vergleich zu älteren 5 V -CPLDs verringert wird.Diese niedrigere Spannung ist in modernen digitalen Mischspannungssystemen nützlich.

• Multispannungs-E/A-Unterstützung

Die E/A -Banken unterstützen mehrere Spannungsstandards, einschließlich 1,5 V, 1,8 V, 2,5 V und 3,3 V. Diese Flexibilität ermöglicht es der CPLD, mit Komponenten, die in unterschiedlichen Spannungsniveaus ohne externe Ebene zu arbeiten, direkt zu senken.

• Hochgeschwindigkeitsbetrieb

Mit einer typischen Ausbreitungsverzögerung von Pin-to-Pin-Ausbreitung von etwa 5,7 Ns (Geschwindigkeitsgrad „-7“) liefert das Gerät eine schnelle, deterministische Leistung.Dies macht es für zeitkritische Anwendungen wie Adressdecodierung, Bus-Schiedsgerichtsbarkeit und Kontrolle geeignet.

• Niedriger Stromverbrauch

Die Coolrunner-II-Serie ist für extrem niedrige Standby-Ströme bekannt, häufig im Mikroamp-Bereich.Diese niedrige statische Leistung, kombiniert mit dynamischen Leistungssparfunktionen, ermöglicht es, dass der XC2C256-7TQ144C effektiv in batteriebetriebenen oder immer-on-Systemen verwendet werden kann.

• Datentechnologie

Diese Funktion ermöglicht es, nicht verwendete Eingänge abzugeben, um unnötige Umschaltungen zu verhindern und den dynamischen Stromverbrauch zu verringern.In Anwendungen, bei denen bestimmte Signale für lange Zeiträume inaktiv sind, ist es wertvoll.

• In-System-JTAG-Programmierung

Das Gerät unterstützt IEEE 1149.1 (JTAG) und IEEE 1532 für das In-System-Programmieren.Dies bedeutet, dass die CPLD konfiguriert, getestet und neu programmiert werden kann, ohne sie aus der Karte zu entfernen, wodurch die Entwicklung und Aktualisierungen vereinfacht werden.

• Fortgeschrittene Taktstruktur

XC2C256-7TQ144C enthält mehrere globale Uhren, Taktivider und doppelt ausgelöste Register.Es bietet auch globale Set/Reset und lokale Takt pro Makrozell, wodurch eine flexible Kontrolle über das Timing und die Synchronisation enthält.

• Schmitt-Trigger-Eingänge

Ausgewählte Eingangsstifte können als Schmitt -Trigger konfiguriert werden, um die Rauschimmunität zu verbessern.Dies ist nützlich, um langsame oder verrückte Eingangssignale zu behandeln, ohne externe Konditionierungsschaltungen hinzuzufügen.

• Flexible Ausgangsfunktionen

Die Ausgänge unterstützen den Betrieb mit drei Staaten, die Steuerung der Sendematen, die Bushaltestelle, die Konfigurationen für Open-Drain und optionale Klimmzüge.Diese Optionen machen es einfach, die CPLD an verschiedene Busstandards und externe Lastbedingungen anzupassen.

• Erweiterte Interconnect Matrix (AIM)

Eine erweiterte Verbindungsmatrix verknüpft Funktionsblöcke effizient und bietet eine vollständige Produkt-Term-Routing über das Gerät.Dies verbessert die Flexibilität der logischen Platzierung und hilft, die vorhersehbare Zeitleistung aufrechtzuerhalten.

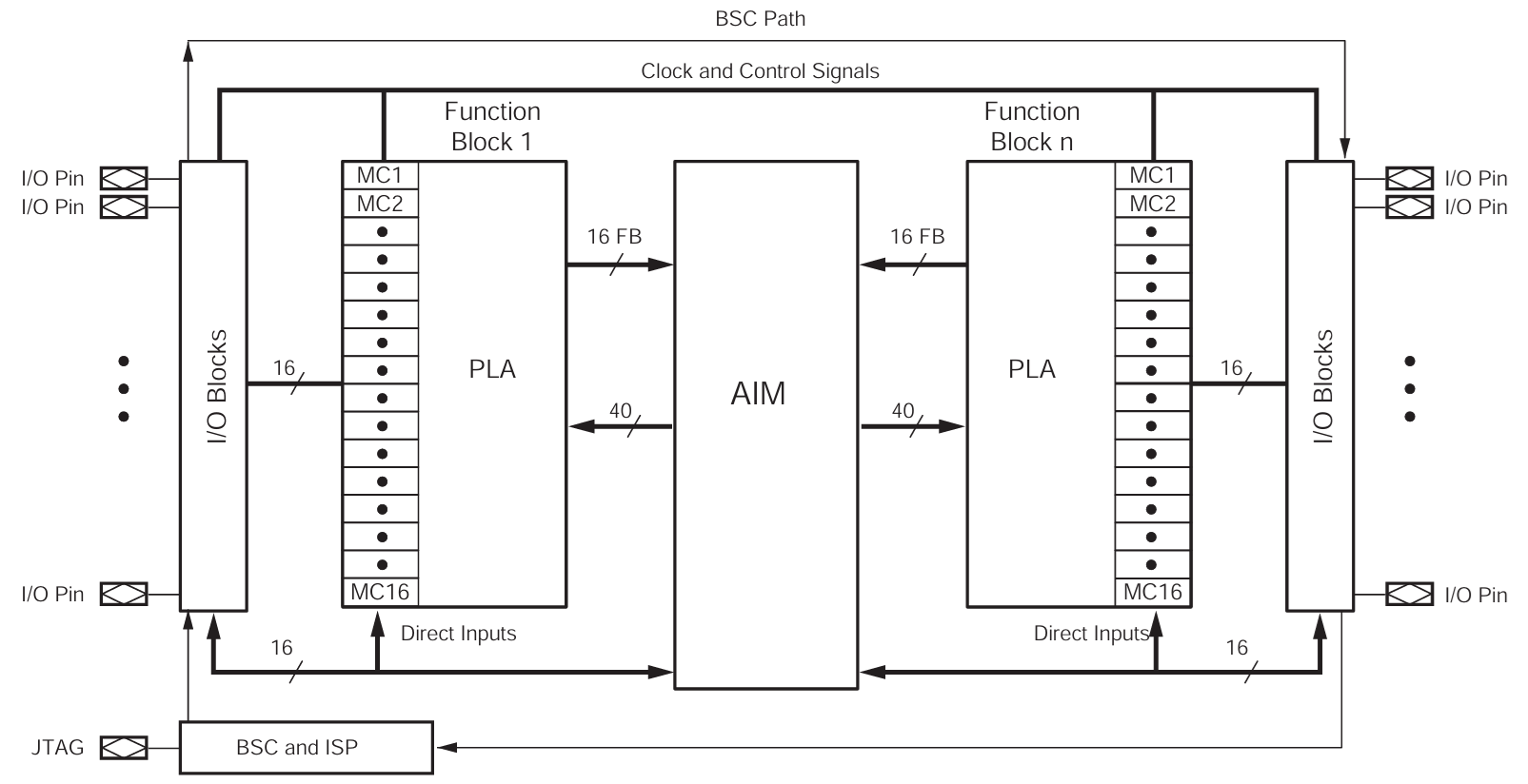

Coolrunner-II-CPLD-Architektur

Die Coolrunner-II-CPLD-Architektur der XC2C256-7TQ144C basiert auf Funktionsblöcken, E/A-Blöcken und einer erweiterten Interconnect-Matrix (AIM).Jeder Funktionsblock enthält Makrozellen und ein programmierbares Logik-Array (PLA), das die benutzerdefinierte Logik implementiert, während das AIM effizient Signale zwischen Blöcken leitet.Die E/A blockiert die interne Logik mit externen Stiften und dedizierten JTAG- und BSC/ISP-Schaltkreisen unterstützen die Programmierung und Prüfung der In-Systeme.Diese strukturierte und miteinander verbundene Architektur ermöglicht eine schnelle, deterministische Leistung mit geringem Stromverbrauch und ist so ideal für Kontrolle, Schnittstellen und Kleberlogik in digitalen Systemen.

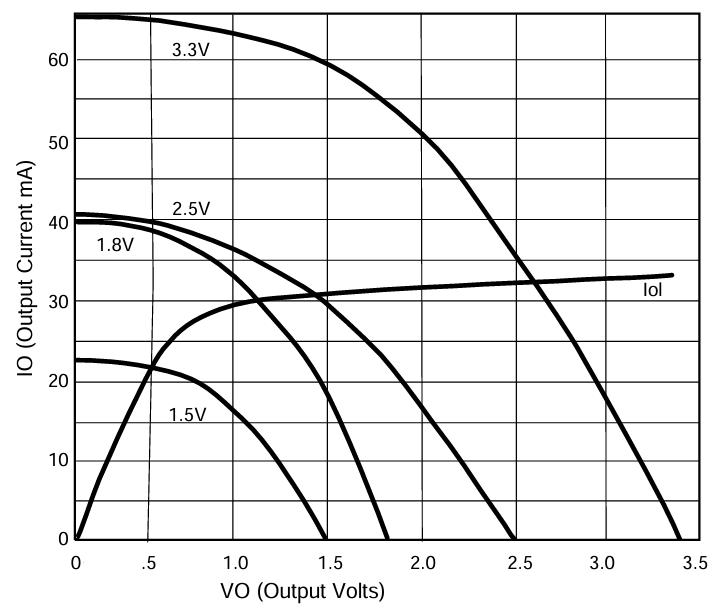

Typische I/V -Kurve für XC2C256

Die typische I/V-Kurve für die XC2C256-7TQ144C zeigt die Beziehung zwischen Ausgangsspannung (VO) und Ausgangsstrom (IO) für verschiedene E/A-Versorgungsspannungen (1,5 V, 1,8 V, 2,5 V und 3,3 V).Wenn die Versorgungsspannung zunimmt, kann das Gerät höhere Ströme beziehen oder sinken, bevor die Ausgangsspannung erheblich sinkt.Dieses Verhalten ist wichtig, um die Antriebsfähigkeit der CPLD bei der Schnittstelle mit externen Komponenten zu verstehen und sicherzustellen, dass die Signalpegel unter Last gültig bleiben.Viele verwenden diese Kurve, um geeignete E/A-Spannungen auszuwählen und einen zuverlässigen Betrieb in Anwendungen sicherzustellen, die spezifische Stromstärken erfordern.

XC2C256-7TQ144C-Spezifikationen

|

Typ |

Parameter |

|

Hersteller |

AMD/Xilinx |

|

Serie |

Coolrunner II |

|

Verpackung |

Tablett |

|

Teilstatus |

Veraltet |

|

Programmierbarer Typ |

In System programmierbar |

|

Verzögerungszeit TPD (1) max |

6.7 ns |

|

Spannungsversorgung - intern |

1,7 V ~ 1,9 V |

|

Anzahl der Logikelemente/Blöcke |

16 |

|

Anzahl der Makrozellen |

256 |

|

Anzahl der Tore |

6000 |

|

Anzahl von i/o |

118 |

|

Betriebstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Montagetyp |

Oberflächenhalterung |

|

Paket / Fall |

144-LQFP

|

|

Lieferantengerätepaket |

144-TQFP (20 × 20) |

|

Grundproduktnummer |

XC2C256 |

XC2C256-7TQ144C-Anwendungen

1. Kleberlogik und Schnittstellenüberbrückung

Der XC2C256-7TQ144C ist ideal für die Implementierung der Kleberlogik, die Signale zwischen verschiedenen digitalen Komponenten verbindet und koordiniert.Es kann Funktionen wie Adressdecodierung, Bus -Schiedsgerichts- und Protokolltranslation erledigen, wodurch eine reibungslose Kommunikation zwischen Mikrocontrollern, Speicher, Sensoren und anderen Peripheriegeräten ermöglicht wird.Die vorhersehbaren Zeitverzögerungen und die schnellen Verzögerungen bei Pin-to-Pin gewährleisten selbst in komplexen Platinenkonstruktionen zuverlässige Schnittstellen.

2. Geräte mit geringer Leistung und batteriebetriebenen Geräten

Dank seiner Fast Zero Power (FZP) -Technologie und sehr niedrigem Standby-Strom ist diese CPLD für tragbare und batteriebetriebene Elektronik sehr geeignet.Es kann kontinuierlich angetrieben werden und gleichzeitig minimaler Energie verbrauchen und es perfekt für die ständige Kontrolle oder Überwachung von Schaltkreisen ist.Sie können die Stromverbrauch mit Funktionen wie Datagate weiter reduzieren, wodurch dynamische Schaltungen minimiert werden, wenn Eingänge inaktiv sind.

3. Kontrolllogik und Sequenzierung

Das Gerät zeichnet sich aus der Implementierung von Finite -Status -Maschinen, der Timing -Steuerung und der Signalsequenzierung in vielen eingebetteten Systemen aus.Die deterministische, nichtflüchtige Architektur ermöglicht es der Steuerlogik, unmittelbar nach dem Einschalten ohne Konfigurationsverzögerungen aktiv zu werden.Dies macht es zu einer starken Wahl für das Zurücksetzen von Logik, Handshaking-Schaltungen und andere zeitkritische Kontrollaufgaben.

V.

In eingebetteten Designs kann der XC2C256-7TQ144C als anpassbarer Support-Chip fungieren, der spezielle Schnittstellen implementiert oder die Funktionen eines Mikrocontrollers erweitert.Es kann Kommunikationsprotokolle wie SPI, I²C oder UART verarbeiten, Chip -Auswahl erzeugen oder Interrupt -Routing verwalten.Durch die Auslastung dieser Funktionen von der CPU vereinfacht dies die Entwicklung der Firmware und verbessert die Gesamtsystemleistung.

XC2C256-7TQ144C Ähnliche Teile

|

Spezifikation |

XC2C256-7TQ144C |

XC2C256-7TQ144I |

XC2C256-7TQG144I |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

Gerätefamilie |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

|

Logikdichte (Makrozellen) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Paketart |

TQFP-144 |

TQFP-144 |

TQFP-144 (Pb-frei) |

VQFP-100 |

VQFP-100 (Pb-frei) |

TQFP-144 |

|

Geschwindigkeitsqualität |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (schneller) |

|

Temperaturbereich |

Kommerziell (0 - 70 ° C) |

Industriell (-40-85 ° C) |

Industriell (-40-85 ° C) |

Kommerziell (0 - 70 ° C) |

Kommerziell (0 - 70 ° C) |

Kommerziell (0 - 70 ° C) |

|

E/O -Pin -Zählung |

118 |

118 |

118 |

80 |

80 |

118 |

|

Kernspannung (VCC) |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

|

E/A -Spannungsunterstützung |

1,5 V - 3,3 V. |

1,5 V - 3,3 V. |

1,5 V - 3,3 V. |

1,5 V - 3,3 V. |

1,5 V - 3,3 V. |

1,5 V - 3,3 V. |

|

Compliance / PB-frei |

Standard |

Standard |

Pb-frei / rohs |

Standard |

Pb-frei / rohs |

Standard |

|

Unterschiede |

Ausgangswerte kommerzielle Version |

Industrie -Temperaturversion |

Industrielle + pb-freie Version |

Kleineres Paket, weniger I/O |

PB-freie kleinere Version |

Schnellere Timing -Version |

XC2C256-7TQ144C-Programmierschritte

Das Programmieren des XC2C256-7TQ144C ist ein einfacher Prozess, bei dem Ihr Design vorbereitet, die Programmierdatei generiert und durch JTAG in die CPLD geladen wird.Wenn Sie jedem Schritt sorgfältig befolgen, können Sie eine erfolgreiche Konfiguration und einen ordnungsgemäßen Gerätevorgang auf Ihrer Karte sicherstellen.

1. Design und Synthese

Sie beginnen Ihr Logikdesign mithilfe von HDL (VHDL oder Verilog) oder einem schematischen Eintrag.Nach Abschluss des Designs führen Sie den Syntheseprozess aus, der Ihre Logik in die interne Struktur des Geräts von Makrozellen und Verbindungen umwandelt.Dieser Schritt stellt sicher, dass Ihr Design mit der XC2C256 -Architektur kompatibel ist und die Implementierung bereit ist.

2. Platz & Route / Implementierung (Anpassung)

Als nächstes führen Sie Orte und Route aus, auch als Anpassung bezeichnet, das Ihre synthetisierte Logik den tatsächlichen physischen Makrozellen und Routing -Ressourcen innerhalb der CPLD zuweist.Das Tool überprüft Zeiteinschränkungen, löst die Ressourcenverbrauch und optimiert die Pfade, um die Leistung Ihres Designs zu erfüllen.Dies stellt sicher, dass die Schaltung zuverlässig ausgeführt wird, sobald sie in das Gerät programmiert sind.

3.. Programmierdatei generieren

Sobald die Implementierung abgeschlossen ist, generieren Sie die Programmierdatei (Bit-, Jam- oder SVF -Format), die die genauen Konfigurationsdaten für das Gerät enthält.Diese Datei stellt dar, wie jede Makrozell, Verbindung und I/A für die Implementierung Ihrer Logik eingerichtet ist.Es wird vor der Vorbereitung dieser Datei benötigt, bevor Sie mit der tatsächlichen Geräteprogrammierung fortfahren.

4. JTAG / In-System-Programmierung

Schließlich verbinden Sie das Gerät mit einem JTAG -Programmierkabel mit Ihrem PC und öffnen das Xilinx Impact -Tool (oder das Äquivalent).Anschließend laden Sie die generierte Programmierdatei und laden sie in den XC2C256-7TQ144C durch die JTAG-Pins (TDI, TDO, TCK, TMS) herunter.Sobald der Vorgang abgeschlossen ist, wird die CPLD sofort mit Ihrer programmierten Logik gearbeitet, ohne einen Stromzyklus oder einen externen Konfigurationsspeicher zu erfordern.

XC2C256-7TQ144C Vor- und Nachteile

Vorteile

• Sehr niedriger Standby-Strom, ideal für batteriebetriebene Konstruktionen.

• Instant-On-Betrieb ohne Konfigurationsverzögerung.

• Vorhersehbares Timing für die leichtere Entwurfsschließung.

• Ersetzt mehrere diskrete Logikchips, Sparen und Kosten.

• Unterstützt mehrere E/A -Spannungen ohne externe Schalthebel.

Nachteile

• Begrenzte Logikkapazität im Vergleich zu größeren CPLDs oder FPGAs.

• Keine eingebauten DSP-, RAM- oder Hochgeschwindigkeits-Transceiver.

• Obsolet werden, die zukünftige Beschaffung schwieriger machen.

• Decke niedrigerer Leistung für Hochgeschwindigkeitsanwendungen.

• Weniger Routing -Flexibilität für komplexe oder unregelmäßige Konstruktionen.

XC2C256-7TQ144C-Verpackungsabmessungen

|

Typ |

Parameter |

|

Paketart |

TQFP-144 |

|

Paketkörpergröße |

20 mm × 20 mm |

|

Lead Pitch |

0,5 mm |

|

Anzahl der Stifte |

144 |

|

Pakethöhe (max) |

1,4 mm |

|

Packungsdicke (nominal) |

1,0 mm |

|

Bleilänge |

0,45 mm ~ 0,75 mm |

|

Bleibreite |

0,17 mm ~ 0,27 mm |

|

Montagetyp |

Oberflächenhalterung |

|

Lieferantengerätepaket |

144-TQFP (20 × 20) |

XC2C256-7TQ144C Hersteller

Der XC2C256-7TQ144C wird von hergestellt von Xilinx, ein führendes Unternehmen in programmierbaren Logiklösungen.Xilinx ist weithin für wegweisende FPGA- und CPLD-Technologien anerkannt und bietet zuverlässige und leistungsstarke Geräte für industrielle, gewerbliche und Verbraucheranwendungen.Heute arbeitet Xilinx als Teil von AMDweiterhin fortschrittliche programmierbare Logikprodukte mit starken langfristigen Unterstützung und Innovation.

Abschluss

Der XC2C256-7TQ144C ist für seinen Stromverbrauch, die schnelle deterministische Leistung und die Multispannungs-E/A-Flexibilität heraus und macht es zu einer zuverlässigen Wahl für moderne digitale Designs.Die ausgewogene Kombination von 256 Makrocells, 118 E/A -Stiften und fortgeschrittener Interconnect -Architektur unterstützt eine breite Palette der Funktionen zur Steuerung, Schnittstelle und Kleber.Mit Unterstützung für In-System-Programmierung, Datensparfunktionen und robusten E/A-Konfigurationen integriert sie reibungslos in eingebettete Systeme und Mischspannungsumgebungen.

Datenblatt PDF

XC2C256-7TQ144C-Datenblätter:

Über uns

ALLELCO LIMITED

Weiterlesen

Schnelle Anfrage

Bitte senden Sie eine Anfrage, wir werden sofort antworten.

Häufig gestellte Fragen [FAQ]

1. Benötigt der XC2C256-7TQ144C externe Konfigurationsspeicher?

Einer seiner Vorteile ist der sofortige Betrieb.Die Konfiguration wird intern gespeichert, sodass sie ohne externe Abschlussball- oder Flash -Speicher bereitgestellt werden kann.

2. Welche Programmierwerkzeuge sind mit XC2C256-7TQ144C kompatibel?

Sie können das Gerät mithilfe der Xilinx Impact -Software mit einem JTAG -Programmierkabel programmieren.Viele verwenden auch kompatible JTAG-Programmierer von Drittanbietern, stellen jedoch sicher, dass sie IEEE 1149.1/1532 Standards unterstützen.

3. Kann der XC2C256-7TQ144C mehrere diskrete Logik-ICs in Ihrem Design ersetzen?

Ja.Mit seinen 256 Makrocells und flexiblen E/A kann diese CPLD mehrere Kleberlogik- und Steuerungsfunktionen in ein Gerät integrieren, wodurch Sie den Raum und die Anzahl der Komponenten reduzieren können.

4. Ist der XC2C256-7TQ144C für Batterieanwendungen mit geringer Leistung geeignet?

Ja.Dank seiner Fast Zero Power (FZP) -Technologie und sehr niedrigem Standby-Strom ist es ideal für immer Einschaltkreise, tragbare Geräte und lensitive Systeme eingebettet.

5. Können Sie die XC2C256-7TQ144C für die Hochgeschwindigkeitssignalverarbeitung verwenden?

Es ist nicht für Hochgeschwindigkeits-DSP- oder Transceiver-Aufgaben ausgelegt.Während es schnelle Pin-to-Pin-Verzögerungen liefert, eignet es sich am besten für Kontrolle, Schnittstellen und Timing-Logik und nicht für komplexe Datenverarbeitung.

EP2S60F672C4 FPGA: Funktionen, Anwendungen, Programmier- und Datenblatthandbuch

auf 2025/10/4

EPM3256AFC256-7 CPLD-Übersicht: Funktionen, Pinout, Programmierung und Anwendungen

auf 2025/10/3

Beliebte Beiträge

-

Komplexe Anweisungssatzcomputer: Wie verändert sie das Computer?

auf 8000/04/18 147776

-

USB-C-Pinout und Funktionen

auf 2000/04/18 112018

-

Verwenden von Xilinx Unified Simulation Primitive: Ein umfassender Leitfaden für FPGA -Design und -Simulation

auf 1600/04/18 111351

-

Stromversorgungsspannungen in der Elektronik: Bedeutung von VCC, VDD, VEE, VSS und GND

auf 0400/04/18 83777

-

RJ45 -Anschlusshandbuch: Pinbeleg, Kabeltypen und Verwendung

auf 1970/01/1 79571

-

Die ultimative Anleitung zu Farbcodes in modernen elektrischen Systemen

Die Art und Weise, wie unsere elektrischen Systeme Farben verwenden, gilt nicht nur für das Aussehen.Jede Drahtfarbe zeigt nun eine bestimmte Funktion an und erleichtert die Identifizierung und Ver...auf 1970/01/1 66964

-

Leitfaden für Spülventile: Funktion, Symptome, Test und Ersatz für eine optimale Motorleistung

Das Säuberventil ist ein wesentlicher Bestandteil eines Autosystems, mit dem die Luft sauber hält, indem sie Kraftstoffdämpfe verwalten, bevor sie in die Atmosphäre entkommen können.Dies hilft der ...auf 1970/01/1 63104

-

Qualität (q) Faktor: Gleichungen und Anwendungen

Der Qualitätsfaktor oder "Q" ist wichtig, wenn Sie überprüfen, wie gut Induktoren und Resonatoren in elektronischen Systemen funktionieren, die Funkfrequenzen (RF) verwenden.'Q' misst, wie gut ein ...auf 1970/01/1 63041

-

Erreichen der Spitzenleistung mit dem maximalen Stromübertragungssatz

Der maximale Stromübertragungssatz erklärt, wie Energie aus einer Quelle wie einer Batterie oder einem Generator zu einer angeschlossenen Last fließt.Es zeigt die genaue Bedingung, bei der die Last...auf 1970/01/1 54097

-

A23 Batteriespezifikationen und Kompatibilität

Die A23-Batterie ist eine kleine, zylinderförmige Batterie mit hoher Spannung.Auch 23A, 23Ae oder Mn21 genannt, läuft es mit 12 Volt und viel höher als AA- oder AAA -Batterien.Sein besonde...auf 1970/01/1 52186